Аналого-цифровой интерфейс

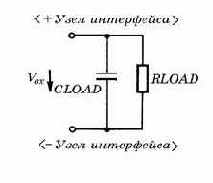

Аналого-цифровые интерфейсы предназначены для преобразования аналогового напряжения в логический уровень. Они имитируют входные каскады цифровых ИС. Их схема замещения показана на рис. 6.3, а. Аналого-цифровые интерфейсы не обязательно включать в схему устройства вручную, так как программа PSpice автоматически расщепляет узел интерфейса и включает устройства интерфейса между аналоговым узлом и входным узлом цифрового устройства. Информация о логическом уровне сигнала на выходе интерфейса А/Ц может направляться двояко:

– в модуль логического моделирования программы PSpice;

– в файл (позднее этот файл может быть просмотрен визуально или использован в качестве источника цифрового сигнала при логическом моделировании в следующем сеансе).

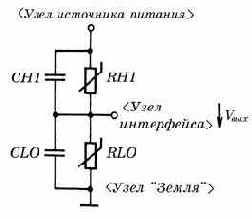

Рис. 6.3. Аналого-цифровой (а) и цифро-аналоговый (б) интерфейсы |

При взаимодействии аналоговых и цифровых компонентов в процессе моделирования описание интерфейса А/Ц (digital output: analog-to-digital) имеет формат

Oxxx <+узел интерфейса> <–узел интерфейса> <имя модели А/Ц>

+ DGTLNET=<имя цифрового узла> <имя модели вход/выход>

При записи логических уровней в файл описание интерфейса А/Ц имеет формат

Oxxx <+узел интерфейса> <–узел интерфейса> <имя модели А/Ц>

+ [SIGNAME=<имя цифрового сигнала>]

Приведем примеры:

O12 ANALOG_NODE DIGITAL_GND DOUT_133

+ DGTLNET=DIG_NODE IO_STD

OVCO 17 0 TO_TTL SIGNAME=VCO_OUT; передача данных в файл

Модель аналого-цифрового интерфейса описывается предложением

.MODEL <имя модели А/Ц> DOUTPUT [<параметры модели>]

Параметры модели аналого-цифрового интерфейса приведны в табл. 6.1.

Таблица 6.1

| Идентификатор | Параметр | Значение по умолчанию | Единица измерения | ||||

| RLOAD | Сопротивление нагрузки | 1/GMIN | Ом | ||||

| CLOAD | Емкость нагрузки | 0 | Ф | ||||

| CHGONLY | Флаг преобразования: 0 – преобразование на каждом шаге по времени; 1 – преобразование при наличии изменения входного напряжения (только при записи в файл) | ||||||

| S0NAME | Имя логического состояния “0” | ||||||

| S0VLO | Нижний уровень напряжения логического “0” | В | |||||

| S0VHI | Верхний уровень напряжения логического “0” | В | |||||

| S1NAME | Имя логического состояния “1” | ||||||

| S1VLO | Нижний уровень напряжения логической “1” | В | |||||

| S1VHI | Верхний уровень напряжения логической “1” | В | |||||

| . . . . . | . . . . . . . . . . . | . . . . . | . . . | ||||

| S19NAME | Имя логического состояния “19” | ||||||

| S19VLO | Нижний уровень напряжения логического состояния “19” | В | |||||

| S19VHI | Верхний уровень напряжения логического состояния “19” | В | |||||

| SXNAME | Имя логического состояния, когда напряжение на узле интерфейса находится вне заданных границ | ? | |||||

| FILE | Имя файла цифрового сигнала (только при записи в файл) | ||||||

| FORMAT | Код формата входного файла цифровых сигналов (только при записи в файл) | 1 | |||||

| TIMESTEP | Интервал дискретизации по времени при с записи в файл | 10 | c | ||||

| TIMESCALE | Масштабный коэффициент при расчете интервала времени TIMESTEP (только при записи в файл) | 1 |

Каждому i- му логическому состоянию соответствует определенный диапазон напряжений

SiVL0...SiVHI. До тех пор пока входное напряжение интерфейса А/Ц Vвх

не выходит за его границы, логическое состояние на выходе интерфейса А/Ц не изменяется. В противном случае входное напряжение будет сравниваться с пороговыми уровнями, начиная с S0VLO, пока оно не попадет в какой-нибудь интервал. Если оно не попадает ни в один интервал напряжений, логическому состоянию интерфейса А/Ц по умолчанию присваивается символ “?” (его можно изменить с помощью параметра SXNAME).

При взаимодействии с модулем логического моделирования программы PSpice имена логических состояний должны быть “0”, “1”, “X”, “R”, “F” или “Z” (однако состояние “Z” обычно не используется, так как состояние высокого импеданса не определяет уровень напряжения).

Параметры TIMESCALE, FILE, CHGONLY

и FORMAT используются только при записи цифрового сигнала в файл. Параметр TIMESTEP

определяет точность установления момента времени изменения логического состояния. При расчете переходных процессов в аналоговых цепях время интегрирования не может превышать значение TIMESTEP. По умолчанию этот параметр принимает меньшее из значений 1 нс или 1/DIGFREQ (параметр DIGFREQ устанавливается по директиве .OPTIONS). Моменты времени, в которые записываются значения выборок сигнала, равны целым значениям величин

k = TIMESCALE·TIME/TIMESTEP,

где TIME – текущее время моделирования, k – номер отсчета. По умолчанию TIMESCALE=1. Для экономии машинного времени следует назначать значение параметра TIMESTEP, исходя из скорости изменения напряжения.

При записи дискретизированного сигнала в файл его имя указывается в опции

SIGNAME=<имя файла>

Если эта опция опущена, то в качестве имени файла будет принято имя интерфейса А/Ц Oxxx без первого символа O.

Логическое состояние интерфейса А/Ц можно просмотреть с помощью программы Probe, указывая в качестве имени переменной B(Oxxx), см.

комментарий к интерфейсу Ц/А.

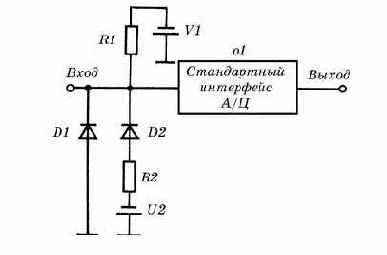

Моделирование входной цепи реального цифрового компонента с помощью линейной RС-цепи, как показано на рис. 6.3, а, не всегда обеспечивает достаточную точность расчетов. Поэтому пользователь должен иметь в своем распоряжении несколько моделей входных цепей логических компонентов, оформляя их в виде макромоделей. В качестве примера на рис. 6.4 представлена нелинейная модель входной цепи логических элементов ТТЛ, к которой подключено стандартное устройство сопряжения типа Oxxx.

Рис. 6.4. Нелинейная модель входной цепи цифрового компонента |