Пример моделирования

В качестве примера моделирования смешанных аналого-цифровых цепей с обратной связью выберем импульсный фазовый детектор (ФД) [8] (рис. 6.19). В его состав входят два RS-триггера X1, X2 типа 133ТМ2, на входы синхронизации которых подключены два источника импульсных напряжений V1, V2 (на входах D и S постоянно установлен уровень “1”). Выходные сигналы триггеров управляют транзисторными ключами, заряжающими емкости С10, С12, входящие в состав сглаживающего фильтра импульсной фазовой автоподстройки (ИФАП). При подаче отпирающего импульса на вход ключа на транзисторах Q1, Q3 потенциал выходного узла 13 увеличивается, а при отпирании другого ключа на транзисторе Q2 – уменьшается. Сброс триггеров производится по сигналу с выхода схемы НЕ–ИЛИ в момент перекрытия во времени входных импульсов. Задержка сброса определяется временем переключения триггеров и вентиля НЕ–ИЛИ и запаздыванием в цепочке R4, C8.

|

Рис. 6.19. Импульсный фазовый детектор |

Приведем задание на моделирование импульсного фазового детектора:

Pulse frequency detector

X1 $D_HI 2 40 $D_HI 3 $D_NC 133TM2

X2 $D_HI 2 41 $D_HI 5 $D_NC 133TM2

X3 3 5 6 133LA3

.PARAM TAU1=0ns TAU2=50ns

V1 40 0 PULSE (0 5 {10ns+TAU1} 1ns 1ns 98ns 200ns)

V2 41 0 PULSE (0 5 {10ns+TAU2} 1ns 1ns 98ns 220ns)

VP 8 0 20V

Q1 7 5 10 KT312A

Q2 13 11 12 KT312A

Q3 13 7 9 KT326B

R4 6 2 100

R5 3 11 470

R6 8 7 3.3k

R7 10 0 2.2k

R9 8 9 1.5k

R10 12 0 1.5k

R11 14 0 1k

C8 2 0 22pF

C10 13 14 0.01uF

C12 14 0 0.01uF

.TRAN 5ns 10us

.PROBE V(13) V(3) V(5) D(40) D(41) D(3$AtoD) D(6$DtoA)

.LIB digital.lib

.LIB qrus.lib

.END

В директивах .LIB указаны имена файлов библиотек, в которых записаны модели цифровых ИС и биполярных транзисторов. Для источников импульсных входных сигналов V1, V2 заданы неравные периоды повторения, что соответствует режиму биений на выходе ФД.

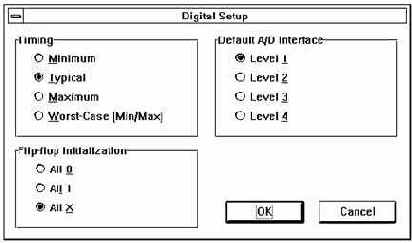

При выполнении моделирования под управлением Schematics по команде Analysis/Setup/Transient задаются параметры режима расчета переходных процессов. Дополнительно в меню Digital Setup (рис. 6.20) в разделе Timing выбираются значения задержек, в разделе Default A/D interface – тип интерфейса А/Ц, устанавливаемый по умолчанию, а в разделе Flip-flop Initialization – начальные состояния триггеров (по умолчанию они имеют неопределенное состояние X).

В текстовом задании на моделирование приведена директива .PROBE V(13) V(3) V(5) D(40) D(41) D(3$AtoD) D(6$DtoA) для ограничения объема выходного файла данных (имеет расширение имени .dat). При использовании графического ввода схем с помощью Schematics эквивалентные результаты достигаются при выборе в меню команды Analysis/Probe Setup опции Data Collection/At Markers Only – в выходной файл будут переданы только данные о переменных, помеченных маркерами.

Рис. 6.20. Установка параметров моделирования цифровых устройств |

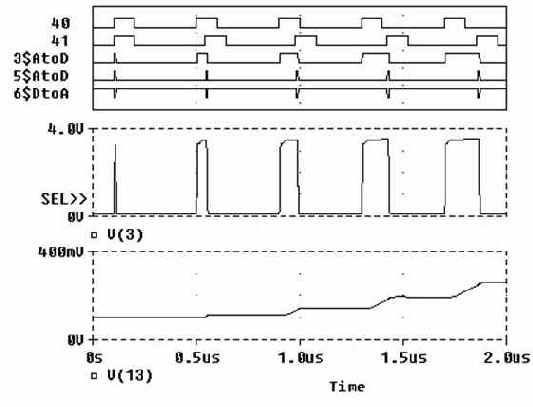

Результаты моделирования показаны на рис. 6.21, полученном с помощью программы Probe. На верхнем экране показаны логические уровни входных сигналов в узлах 40, 41, 3 5 6 и 2 , на среднем – аналоговые напряжения на входах ключей в узлах 3, 5, на нижнем – напряжение на выходе ФД в узле 13, позволяющее оценить период и амплитуду биений. Расчет переходных процессов, представленных на рис. 6.21, занимает 10 с на ПК c процессором 486DX4/100 МГц.

Рис. 6.21. Результаты моделирования |

В заключение отметим, что для реализации графического ввода схем аналого-цифровых устройств с помощью Schematics цифровые компоненты должны быть представлены в виде макромоделей, составляемых на основе справочных данных [24, 28].